-

دسته: رشته الکترونیکفرمت : word | صفحات : 63قیمت: 8000 تومان

773 views

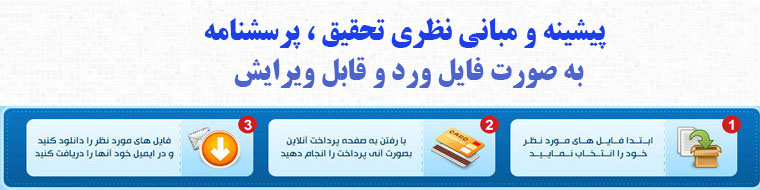

پیشینه تحقیق معرفی گیت قابل برنامه ریزی میدانی FPGA و حافظه ها شامل SRAM و DRAM و ساختار داخلی سلول حافظه دارای ۶۳ صفحه می باشد فایل پیشینه تحقیق به صورت ورد word و قابل ویرایش می باشد. بلافاصله بعد از پرداخت و خرید لینک دنلود فایل نمایش داده می شود و قادر خواهید بود آن را دانلود و دریافت نمایید . ضمناً لینک دانلود فایل همان لحظه به آدرس ایمیل ثبت شده شما ارسال می گردد.

فهرست مطالب

۲-۱- معرفی گیت قابل برنامهریزی میدانی FPGA ۴

۲-۲- معرفی حافظه ها شامل SRAM و DRAM ۵

۲-۳- ساختار داخلی سلول حافظه ۷

۲-۳-۱ سلول حافظه ۶ ترانزیستوری پایه ۷

۲-۳-۲ نوشتن داده در سلول ۸

۲-۳-۳ نگهداری داده در سلول ۱۰

۲-۳-۴ خواندن داده از سلول ۱۱

۲-۴- معرفی حاشیه نویز ایستای خواندن و جریان سلول ۱۲

۲-۵- سلول بهبود یافته ۱۵

۲-۵-۱ نوشتن در سلول جدید ۱۶

۲-۵-۲ نگهداری داده در سلول جدید ۱۹

۲-۵-۳ خواندن داده از سلول جدید ۲۱

۲-۶- بررسی سلول جدید ارائه شده از دیدگاه تاخیر در خواندن و نوشتن ۲۲

۲-۶-۱ تأخیر نوشتن در سلول ۲۲

۲-۶-۲ تاخیر خواندن داده از سلول ۲۶

۲-۷- بررسی جریان نشتی در سلول حافظه ۳۰

۲-۸- بررسی برخی سلول های ارائه شده ۳۳

۲-۸-۱ سلول با نشتی پایین و آگاه به صفر ۳۷

۲-۸-۲ سلول SRAM سخت شده نسبت به صفر ۳۸

۲-۹- بررسی سلول بهبودیافته ۴۲

۲-۱۰- بررسی چالش جریان نشتی ۵۵

منابع و ماخذ ۶۳

فهرست منابع فارسی ۶۳

فهرست منابع انگلیسی ۶۳

منابع

عزیزی مزرعه، آرش. ۱۳۹۰٫ پیاده سازی سیستم های چندعامله تحمل پذیر خطا بر روی سخت افزارهای قابل پیکربندی. طرح دانشگاه آزاد اسلامی واحد سیرجان.

عزیزی مزرعه، آرش.، محمدتقی منظوری. و محمد نوراللهی رومنی. ۱۳۸۷٫ یک سلول پنج ترانزیستوری جدید SRAM برای کاربرد با سرعت زیاد و تراکم بالا. نشریه علمی پژوهشی انجمن کامپیوتر ایران. شماره ۱٫

دکتر آسمانی. جزوه خودآموز نرم افزار HSPICE.

Takeda, K., Y. Hagihara, Y. Aimoto, M. Nomura, Y. Nakazawa, T. Ishii, and H. Kobatake, “A read-static-noise-margin-free SRAM cell for low-VDD and high-speed applications,” IEEE Journal of Solid-State Circuits, Vol. 41, No. 1, 2006.

Zhang, K., U. Bhattacharya, Z. Chen, F. Hamzaoglu, D. Murray, N. Vallepalli, Y. Wang, B. Zheng, and M. Bohr, “SRAM Design on 65-nm CMOS Technology With Dynamic Sleep Transistor for Leakage Reduction,” IEEE J. Solid-State Circuits, Vol. 40, No. 4, 2005.

Osada, K., Y. Saitoh, E. Ibe, and K. Ishibashi, “7-fA/cell tunnel-leakage-suppressed 16-Mb SRAM for handling cosmic-ray-induced multierrors,” IEEE J. Solid-State Circuits, Vol. 38, No. 11, 2003.

Rabaey, J. M., A. Chandrakasan, and B. Nikolic, Digital Integrated Circuits: A Design Perspective, 2nd ed., Prentice Hall, 2002.

Seevinck, E., F.J List, and J. Lohstroh, “Static-noise margin analysis of MOS SRAM cells,” IEEE Journal of Solid-State Circuits, Vol. 22, No. 2, 1987.

Azizi Mazreah, A., M.T. Manzuri Shalmani, Low-leakage soft error tolerant dual-port SRAM cells for cache memory applications, Elsevier Microelectronics Journal 10 (2012) 1016 /j.mejo.2012.07.005.

Azizi, N., F.N. Najm, A. Moshovos, Low-leakage asymmetric-cell SRAM, IEEE Transactions on Very Large Scale Integration Systems 11 (4) (2003).

Ebrahimi, H., M. Saheb Zamani, H.R. Zarandi, Mitigating soft errors in SRAMbased FPGAs by decoding configuration bits in switch boxes, Elsevier Microelectronics Journal 42 (2011).

Anderson, J. H., and F. N. Najm, “Active leakage power optimization for FPGAs”, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems Vol. 25 No. 3, 2006.

Asadi, Gh. and M.B. Tahoori, Soft error rate estimation and mitigation for SRAM based FPGAs, in: Proceeding of the 13th International Symposium on Field-programmable Gate Arrays, 2005.

Gill, B.S., G. Papachristou, and F.G. Wolff, A new asymmetric SRAM cell to reduce soft errors and leakage power in FPGA, in: Design Automation & Test in Europe Conference & Exhibition, 2007.

Kotabe, A., K. Osada, N. Kitai, M. Fujioka, S. Kamohara, M. Moniwa, S. Morita, and Y. Saitoh, “A Low-Power Four-Transistor SRAM Cell With a Stacked Vertical Poly-Silicon PMOS and a Dual-Word-Voltage Scheme,” IEEE J. Solid-State Circuits, Vol. 40, No. 4, 2005.

۲-۱- معرفی گیت قابل برنامهریزی میدانی FPGA

فن آوری آرایه سوئیچ فیوزهای قابل برنامه ریزی چند باره، انقلابی نوین را در عرصه طراحی دیجیتال به وجود آورد که مفهوم طراحی دیجیتال را دچار تحولی عظیم در عرصه های دیدگاه معماری، حجم طراحی، سرعت و نوع نگرش به طراحی دیجیتال نموده است. طوری که امروزه FPGAها (آرایه های گیتی قابل برنامه ریزی میدانی) یک بوم نقاشی سفید را در اختیار طراح قرار می دهند که به او اجازه می دهد تا طراحی دیجیتال خود را آنچنان که می خواهد و با هر حجم و پیچیدگی لازم، طراحی و سپس به جای انتخاب IC های استاندارد و جدا از هم و کنار هم قراردادن آنها در روی یک مدار و وصل کردن آنها از طریق یک بورد مدار چاپی، با استفاده از یکی از زبان های توصیف سخت افزاری نظیر VHDL، هر یک از قطعات دیجیتالی مورد نیاز را نوشته و با وصل کردن نرم افزاری آنها، سرانجام فایل کامپایل شده نهایی را از طریق یک رابط سخت افزاری بر روی یک بسته سخت افزاری خام با تعداد پایههای مورد نیاز برنامهریزی کرده و از این IC جدید “خود ساخته” استفاده کند. FPGA ها نسل جدید مدارهای مجتمع دیجیتال قابل برنامهریزی هستند که عبارت FPGA از سر کلمههای Field Programmable Logic Gate Array گرفته شده است. سرعت اجرای توابع منطقی درFPGA ها بسیار بالا و در حد نانو ثانیه است. اگر بخواهیمFPGA ها را به طور ساده تشریح کنیم، عبارت است از یک تراشه که از تعداد بالایی بلوک های منطقی، خطوط ارتباطی و پایه های ورودی/ خروجی تشکیل شده است که به صورت آرایه ای در کنار یکدیگر قرار دارند. خطوط ارتباطی که وظیفه آنها ارتباط بین بلوکهای منطقی است از سوئیچهای قابل برنامه ریزی تشکیل شدهاند. این سوئیچها بسته به نوعی که دارند، برخی تنها یکبار برنامهریزی هستند و برخی به تعداد دفعات زیادی برنامهریزی میشوند.

بلوکهای منطقی نیز دارای انواع مختلفی هستند که عموما توسط آلمانی پایه، تمامی توابع منطقی را ایجاد میکنند. به عنوان مثال بلوکهای منطقی در خانواده ACT-1 از شرکت Actel، با پایه مالتی پلکسری عمل میکنند. به این معنا که توسط مالتی پلکسر، توانایی ایجاد توابع منطقی مختلف را دارند.

البته تعداد ورودیهای هر بلوک منطقی متفاوت است و به نوع FPGA مربوط می شود. به عنوان مثال بلوکهای منطقی در خانوادهء ACT-1، از نوع ۸ ورودی است. البته در برخی موارد به بلوکهای منطقی سلولهای منطقی نیز گفته می شود. بلوک دیاگرام یک FPGA به طور ساده در شکل ۲-۱ نشان داده شده است.

البته بسیاری از سلولهای منطقی بر اساس جداول LUT ساخته می شوند. LUT از تعدادی سلولهای حافظه SRAM تشکیل میشود که در هنگام برنامهریزی FPGA، مقداردهی میشوند. به طور خلاصه LUT عبارت است از تولید توابع آماده برای استفاده در سلولهای منطقی.

پیادهسازی توابع مختلف نیز به وسیله در کنار هم قرار گرفتن بلوکهای منطقی و همچنین تنظیم ارتباط بین هر بلوک و به عهده گرفتن پردازش اطلاعات توسط هر بخش انجام میشود.

۲-۲- معرفی حافظه ها شامل SRAM و DRAM

در یک دسته بندی کلی حافظه هایی که در سیستمهای الکترونیکی استفاده می شوند به دو نوع حافظههای مغناطیسی (مثل فلاپی دیسک ها و دیسک های سخت) و نیمه هادی تقسیم می شوند. در اینجا هدف ما بررسی حافظههای نیمه هادی است. حافظههای نیمه هادی که بر خلاف حافظههای مغناطیسی فاقد اجزای متحرک و مکانیکی هستند از آرایههایی از سلولهای حافظه تشکیل شدهاند که این آرایهها بسته به نوع حافظه از تعدادی عنصر الکترونیکی مثل ترانزیستور و خازن تشکیل شدهاند.

RAM سرنام Random Access Memory یا حافظه ی با دستیابی تصادفی است که البته این نامگذاری حافظهها تا حدودی جنبه ی تاریخی دارند و با توجه به اینکه دو نوع حافظه ی دیگر هم دارای این ویژگی هستند این نام ها تا حدودی مخدوش شده اند ولی همچنان از این اسامی استفاده می شود. مهمترین ویژگی RAM ها ناپایدار بودن اطلاعات موجود در آنهاست یعنی تا زمانی که تغذیه به آن ها وصل باشد اطلاعات نگهداری می شوند RAM ها به دو نوع DRAM و SRAM تقسیم میشوند که از لحاظ الکترونیکی تفاوت آنها در اجزای سازند آنهاست DRAM مخفف Dynamic RAM یا RAM پویا میباشد که دلیل آن استفاده از خازن در ساختمان این نوع حافظه میباشد بنابراین برای حفظ اطلاعات در آن باید اطلاعات موجود در سلولهای حافظه نوسازی شوند تا خازنها شارژ شوند. اما حافظه هایSRAM یا Static RAM از اجزایی به نام فلیپ فلاپ ها تشکیل شدهاند و برای حفظ اطلاعات فقط نیاز به تغذیه دارند. واضح است که از لحاظ مداری حافظهها DRAM از پیچیدگی کمتری در مقایسه با SRAM ها برخوردارند زیرا هر فلیپ فلاپ خود از چندین ترانزیستور تشکیل شده است. از طرف دیگر حافظهی DRAM به دلیل وجود خازن، بر خلاف نوع دیگر توانایی نگهداری اطلاعات را در غیاب تغذیه در حدود چند میلی ثانیه دارا می باشد. اما مهترین ویژگی SRAM در مقایسه باDRAM سرعت بالاتر (حدود ۴ برابر) آن است زیرا DRAM در مدت نوسازی قادر به نوشتن یا خواندن اطلاعات نیست. بنابراین از SRAM ها معمولاً در Cache پردازندهها استفاده می شود در این تحقیق ما به بررسی و کار بر روی حافظه های SRAM میپردازیم.

IOB نشان دهنده بلوکهای ورودی و خروجی میباشد.

LB نشان دهنده بلوکهای منطقی قابل برنامه ریزی میباشند.

همانطور که ذکر شد حافظههای SRAM خود از مجموعهای از ترانزیستورها ساخته شدهاند که این ساختار با توجه به موارد ذکر شده دارای سه حالت عملکرد شامل عملیات خواندن نگه داری داده و نوشتن می باشد. در ادامه به بررسی ساختار داخلی سلول های حافظه SRAM، بررسی جریان نشتی در این سلول، سلولهای بهبود یافته ارائه شده و در نهایت بررسی ساختار سلولهای بهبود یافته میپردازیم.

۲-۳- ساختار داخلی سلول حافظه

۲-۳-۱ سلول حافظه ۶ ترانزیستوری پایه

هسته اصلی حافظهSRAM را آرایهای از سلولها تشکیل میدهد که این سلول در حالت پایه از ۶ ترانزیستور ساخته شده است و قسمت زیادی از مساحت سلول را اشغال میکند به همین دلیل مساحت اشغال شده توسط یک سلول عامل تعیین کنندهای در طراحی یک SRAM با تراکم بالا میباشد.

این سلول پایه ۶ ترانزیستوری دارای مشکلات و معایبی ازجمله سرعت، حاشیه نویز ایستا و جریان نشتی میباشد که در این عوامل نیز در ارتباط با یکدیگر میباشند. در ادامه به بررسی عوامل موثر در عملکرد این سلول و بررسی سلولهای ارائه شده ای که هر یک با هدف بهبود یکی از عوامل ذکر شده طراحی و ارایه شدهاند میپردازیم. درسلول پایه که ساختار شماتیک مداری آن در شکل ۲-۳ آمده است مشاهده میکنیم که این سلول دارای ساختار کلی که شامل دو بخش معکوس کننده که هر بخش از دو ترانزیستور ماسفت یکی از نوع NMOS و دیگری از نوع PMOS میباشد که در شکل ۴-۲ ساختار این معکوس کننده آورده شده است.

وظیفه بخش معکوس کننده در سلول ۶ ترانزیستوری پایه نگهداری داده ورودی و خوانده شده و ارائه آن به رشته بیتی که برای آدرس دهی و مشخص کردن ورودی جدول جستجو است، می باشد.

تمامی فایل های پیشینه تحقیق و پرسشنامه و مقالات مربوطه به صورت فایل دنلودی می باشند و شما به محض پرداخت آنلاین مبلغ همان لحظه قادر به دریافت فایل خواهید بود. این عملیات کاملاً خودکار بوده و توسط سیستم انجام می پذیرد. جهت پرداخت مبلغ شما به درگاه پرداخت یکی از بانک ها منتقل خواهید شد، برای پرداخت آنلاین از درگاه بانک این بانک ها، حتماً نیاز نیست که شما شماره کارت همان بانک را داشته باشید و بلکه شما میتوانید از طریق همه کارت های عضو شبکه بانکی، مبلغ را پرداخت نمایید.

جستجو پیشرفته

دستهها

- حقوق بین الملل

- دستهبندی نشده

- رشته MBA

- رشته آبخیزداری

- رشته آمار

- رشته آموزش ابتدایی

- رشته ادبیات

- رشته ارتباطات

- رشته اقتصاد

- رشته الکترونیک

- رشته باستان شناسی

- رشته برق

- رشته برنامه ریزی درسی

- رشته برنامه ریزی

- رشته برنامه ریزی شهری

- رشته بهداشت

- رشته بهداشت تغذیه

- رشته بیوتکنولوژی

- رشته بیوتکنولوژی دریایی

- رشته پرستاری

- رشته پزشکی

- رشته تاریخ

- رشته تربیت بدنی

- رشته تغذیه

- رشته تکنولوژی آموزشی

- رشته جامعه شناسی

- رشته جغرافیا

- رشته حسابداری

- رشته حقوق

- رشته داروسازی

- رشته دامپروری

- رشته دامپزشکی

- رشته داندانپزشکی

- رشته دریانوردی

- رشته راهور

- رشته روابط بین الملل

- رشته روانشناسی

- رشته ریاضی

- رشته زبان و ادبیات عرب

- رشته زبانشناسی

- رشته زمین شناسی

- رشته زیست شناسی

- رشته ژنتیک

- رشته سینما

- رشته شهرسازی

- رشته شیلات

- رشته شیمی

- رشته صنایع غذایی

- رشته عرفان اسلامی

- رشته علم اطلاعات ودانش شناسی

- رشته علوم اجتماعی

- رشته علوم باغبانی

- رشته علوم تربیتی

- رشته علوم دامی

- رشته علوم سیاسی

- رشته علوم و تکنولوژی پلیمر

- رشته عمران

- رشته فقه

- رشته فلسفه

- رشته فیزیک

- رشته فیزیولوژی جانوری

- رشته فیزیولوژی گیاهی

- رشته کامپیوتر

- رشته کتابداری

- رشته کشاورزی

- رشته گفتاردرمانی

- رشته گیاه پزشکی

- رشته محیط زیست

- رشته مخابرات

- رشته مدیریت بازرگانی

- رشته مدیریت خدمات بهداشتی و درمانی

- رشته مدیریت

- رشته مدیریت آموزشی

- رشته مدیریت اجرایی

- رشته مدیریت بازاریابی

- رشته مدیریت ترافیک

- رشته مدیریت جهانگردی

- رشته مدیریت دولتی

- رشته مدیریت صنعتی

- رشته مدیریت مالی

- رشته مدیریت منابع انسانی

- رشته مدیریت ورزشی

- رشته مشاوره

- رشته معارف اسلامی

- رشته معدن

- رشته معماری

- رشته مکانیک

- رشته منابع طبیعی

- رشته مهندسی ابزار دقیق و اتوماسیون صنایع نفت

- رشته مهندسی چوب و کاغذ

- رشته مهندسی سازه های هیدرولیکی

- رشته مهندسی سیستم های اقتصادی اجتماعی

- رشته مهندسی صنایع

- رشته مهندسی فناوری اطلاعات

- رشته مهندسی گاز

- رشته مهندسی مواد

- رشته مهندسی نرم افزار

- رشته مهندسی نفت

- رشته مهندسی هسته ای

- رشته مهندسی هوا و فضا

- رشته موسیقی

- رشته میکروبیولوژی

- رشته نساجی

- رشته هنر

- رشته هواشناسی

- فیزیولوژی ورزشی

- کارآفرینی

- متفرقه

- مدیریت گردشگری

- مدیریت ورزشی

- مهندسی پلاسما

- مهندسی حمل و نقل دریایی

آخرین بروز رسانی

-

چهارشنبه, ۵ اردیبهشت , ۱۴۰۳

محفوظ می باشد.

محفوظ می باشد.

ارسال نظر